# Objectives of the Course

#### **Workshop theme**

The main aim and motivation of organizing this workshop is to expose the academicians and industry personals to design of adaptive analog systems, using FPAA in the area of Control and measurement systems, Analog signal processing, and rapid prototyping.

### **Topics covered in the Workshop**

- ☐ FPAA

- ☐ EDA Tool & simulation

- FPAA architecture and CAM

- Evaluation board

- ☐ Static Configuration

- Dynamic reconfiguration

- ☐ Filter Design, Signal Processing, Sensor Applications

#### **Outcome of the Workshop**

At the end of the workshop, each participant is expected to have enhanced his/her knowledge on FPAA and its application in the areas of signal processing, control systems, Sensor, Bio-medical applications and rapid prototyping.

# Important date

Last Date of Registration : 20-10-2017 Intimation of Acceptance by Email : 22-10-2017 Course Date : 24-10-2017

### Venue

School of Electrical Sciences Indian Institute of Technology Bhubaneswar Argul, Odisha, India

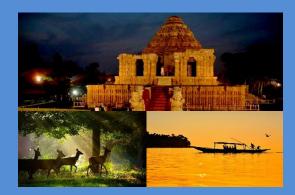

#### About Bhubaneswar

Bhubaneswar is described as a Temple City of India. Sun Temple at Konark, popularly known as Black Pagoda and Lord Jagannath Temple at Puri are world famous for their lively art, excellent architecture and sculpture. Bhubaneswar with its modern buildings and extensive infrastructure perfectly complements its historic surroundings with facilities to cater to every type of visitor, Bhubaneswar makes an ideal tourist destination. Bhubaneswar is well connected by air, rail and road to the rest of India.

Bhubaneswar is famous for Lingaraj temple and Buddhists monuments such as Khandagiri, Udaygir and Ratnagiri. The great Buddhist shrine Dhauli is situated only 8 km away from Bhubaneswar.

The famous Sri Jaganath Temple of Puri and Suntemple of Konark are about 50 km from Bhubaneswar.

Sea beaches at Puri, Konark, Chandipur; Zoo of Nandan Kanan and Chilka Lagoon are world famous tourist attractions.

# Registration

(Participants are limited and shortlist will be on first come first served basis)

Fee:

| Academicians        | 1,500 INR |

|---------------------|-----------|

| Research Scholars   | 750 INR   |

| PG/UG Students      | 500 INR   |

| Internal Candidates | NIL       |

Mode of Payment:

The payment of registration fee should be made by dd/Bank transfer.

(in favor of "CEP, IIT Bhubaneswar" payable at

Bhubaneswar)

A/C no:24282010001960 IFSC Code: SYNB0002428 Bank name: Syndicate bank

Branch Address: IIT Bhubaneswar

Participants can avail their food on payment basis

# Registration Form

| Name (Block Letters):    |

|--------------------------|

| College/Institution name |

| Designation:             |

| Specialization:          |

| Address:                 |

|                          |

|                          |

| Telephone:               |

| Email:                   |

### **Payment Details**

| Draft No      |  |

|---------------|--|

| Amount        |  |

| Issuing Bank: |  |

| Date:         |  |

### Declaration

The information provided is true to the best of my knowledge. If selected, I agree to abide by the rules and regulations of the course.

# Highlights of the Course

### DAY-1 24<sup>th</sup> Oct2017(Tuesday): 09:30 AM-05.00 PM

| 09.30 am - 09.45 am | Introduction            |

|---------------------|-------------------------|

| 09.45 am - 10.00 am | Tea Break               |

| 10.00 am - 10.30 am | Anadigm Designer 2 –EDA |

|                     | Tool                    |

| 10.30 am - 11.30 am | Simulation ( Hand On)   |

| 11.30 am - 12.30 pm | FPAA Configuration      |

| 12.30 am - 02.00 pm | Lunch Break             |

| 02.00 pm - 02.30 pm | IO Pin Configuration    |

| 02.30 pm - 03.15 pm | Static Configuration    |

| 03.15 pm - 03.30 pm | Tea Break               |

| 03.30 pm - 05.00 pm | Audio Signal Processing |

|                     | in FPAA                 |

(Design and Implementation)

#### DAY-2 25th Oct2017(Wednesday): 09:45 AM-05.00 PM

09.45 am – 10.45 am Dynamic Reconfiguration

Various Method( Algorithmic, State-Driven , PC-Driven)

10.45 am – 11.00 am Tea Break

11.00 am – 11.45 am Dynamic Reconfiguration Using

Windows Application ( Hand On)

11.45 am – 12.30 pm Dynamic Reconfiguration

Audio Signal Processing in FPAA

12.30 pm – 02.00 pm Lunch Break

02.00 pm – 03.00 pm Filter Design & Implementation

03.00 pm – 03.15 pm Tea Break

03.15 pm – 05.00 pm FPAA in Sensor Applications

Programme Coordinators:

Dr. D.Ghosh, SES, IIT Bhubaneswar

Dr. M S Manikandan, SES IIT Bhubaneswar

Dr. P.K.S ahu, SES, IIT Bhubaneswar

Janaki raman Srinivasan, Managing Director, Oppila

Microsystems Private Limited

Rajesh R, Embedded Software Engineer, Oppila

Microsystems Private Limited

Natesan S, Design Engineer, Oppila Microsystems

Private Limited

# About Indian Institute of Technology Bhubaneswar

Indian Institute of Technology Bhubaneswar came into existence in July 22, 2008, inheriting the brand name IIT. The Institute is aspiring to be of worthy of its inheritance and at the same time be distinctive and distinguished on its own.

Indian Institute of Technology Bhubaneswar offers several academic programs through its seven academic schools. Each school offers both specialized and interdisciplinary courses. The Institute offers undergraduate programs in engineering branches and postgraduate programs (Master's, Doctoral and Postdoctoral programs) in engineering as well as science disciplines.

The Institute provides an ambience that facilitates research and development leading to creation of knowledge through fundamental and applied research, innovations, and entrepreneurship. The Institute facilitates sponsored and collaborative research with reputed industries, R&D laboratories, universities and institutes globally.

### **Contact Person:**

Dr. P.K Sahu

Coordinator,

FPAA-2017

School f Electrical Sciences

Argul Campus

Indian Institute of Technology Bhubaneswar

Khurda-752050

Odisha, India

E-mail: pks@iitbbs.ac.in